EDA技術與CPLD/FPGA開發(fā)應用簡明教程 賦能計算機軟硬件創(chuàng)新

隨著信息技術的飛速發(fā)展,計算機系統(tǒng)的設計已從傳統(tǒng)的固定功能硬件與通用軟件的結合,逐步邁向高度可定制、軟硬件協(xié)同設計的新階段。在這一進程中,電子設計自動化(EDA)技術以及復雜可編程邏輯器件(CPLD)和現(xiàn)場可編程門陣列(FPGA)扮演了至關重要的角色。本教程旨在為高等院校計算機及相關專業(yè)學生,以及對計算機軟硬件開發(fā)感興趣的工程師,提供一份關于EDA技術與CPLD/FPGA開發(fā)應用的系統(tǒng)性入門指南,闡明其核心原理、開發(fā)流程及在現(xiàn)代計算系統(tǒng)中的廣泛應用。

第一部分:技術基石——EDA、CPLD與FPGA概述

1. 電子設計自動化(EDA)技術

EDA是指利用計算機軟件工具來完成電子系統(tǒng)設計的一系列技術總和。它涵蓋了從系統(tǒng)設計、功能驗證、邏輯綜合、布局布線到物理實現(xiàn)、時序分析、仿真測試的完整流程。EDA工具極大地解放了設計師,使設計超大規(guī)模集成電路(VLSI)和復雜可編程邏輯成為可能,是連接創(chuàng)意與硬件實現(xiàn)的橋梁。

2. 可編程邏輯器件:CPLD與FPGA

- CPLD(復雜可編程邏輯器件):基于乘積項結構,內部由可編程的與陣列、固定的或陣列及宏單元構成。其特點是邏輯資源相對集中,延時確定且可預測,適用于實現(xiàn)復雜度中等、對時序要求嚴苛的組合邏輯和狀態(tài)機。

- FPGA(現(xiàn)場可編程門陣列):基于查找表(LUT)結構,內部包含大量可編程邏輯塊(CLB)、豐富的布線資源和可編程的輸入輸出單元(IOB)。FPGA邏輯容量大,靈活性極高,可通過編程實現(xiàn)從簡單邏輯到復雜處理器內核(如軟核CPU)的各類功能,并支持動態(tài)部分重配置。

兩者共同構成了數(shù)字系統(tǒng)設計的“萬能實驗室”,允許開發(fā)者通過硬件描述語言(HDL)在芯片內部“構造”出所需的專用硬件電路。

第二部分:開發(fā)流程與實踐——從代碼到硬件

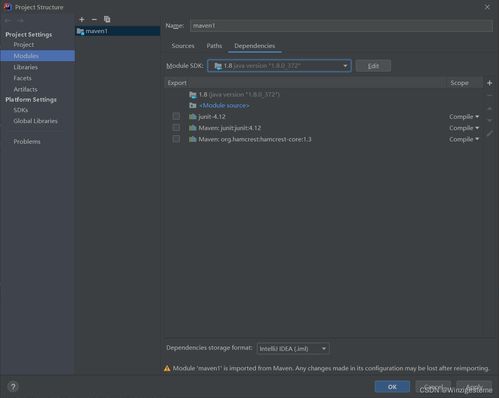

CPLD/FPGA的開發(fā)緊密依賴于EDA工具鏈,其標準流程通常包括以下關鍵步驟:

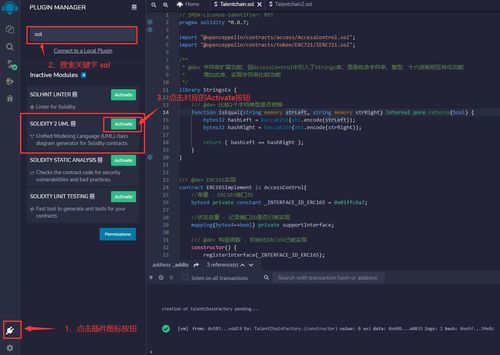

- 設計輸入:使用硬件描述語言(如VHDL或Verilog)進行行為級或寄存器傳輸級(RTL)描述,或利用原理圖、IP核等方式定義系統(tǒng)功能。

- 功能仿真(前仿真):在綜合與布局布線之前,通過軟件仿真驗證設計邏輯的正確性,確保其符合預期行為。

- 邏輯綜合:使用綜合工具將HDL代碼轉換為由基本邏輯門和觸發(fā)器組成的網(wǎng)表,這是一個將高級描述映射到目標器件可用資源的過程。

- 布局布線:EDA工具將綜合后的網(wǎng)表映射到目標CPLD/FPGA芯片的具體邏輯單元和連線資源上,生成具體的物理連接信息。

- 時序仿真(后仿真):在包含器件實際延時信息的網(wǎng)表基礎上進行仿真,驗證設計在真實硬件中能否滿足時序要求(如建立時間、保持時間)。

- 編程下載:將最終生成的配置文件通過下載線纜(如JTAG)燒錄到CPLD/FPGA芯片中,使其具備預定的硬件功能。

第三部分:廣闊的應用天地——驅動計算機軟硬件創(chuàng)新

CPLD/FPGA憑借其并行處理、硬件可重構、低延遲等特性,在計算機軟硬件開發(fā)及應用領域發(fā)揮著不可替代的作用:

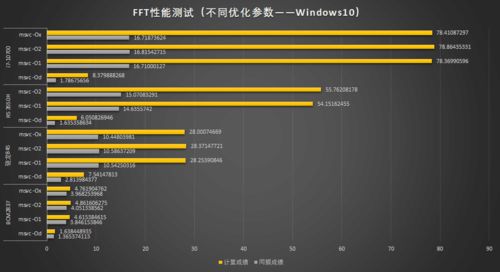

- 硬件加速與協(xié)處理:在數(shù)據(jù)中心、人工智能、高性能計算領域,F(xiàn)PGA被廣泛用于加速特定算法(如深度學習推斷、加解密、視頻編碼),作為CPU的協(xié)處理器,顯著提升能效比和吞吐量。

- 原型驗證與系統(tǒng)集成:在開發(fā)新的處理器、ASIC或復雜系統(tǒng)芯片(SoC)之前,使用FPGA搭建功能原型,進行軟硬件協(xié)同驗證,大幅降低流片風險和成本。

- 接口橋接與協(xié)議實現(xiàn):靈活實現(xiàn)各種標準或自定義的通信接口(如PCIe, USB, Ethernet, DDR內存控制器),在主板設計、工業(yè)控制、網(wǎng)絡設備中承擔“膠合邏輯”和協(xié)議轉換的核心任務。

- 嵌入式系統(tǒng)與可重構計算:將軟核處理器(如Nios II, MicroBlaze)與自定義外設集成在單一FPGA芯片內,構成一個完整的可重構片上系統(tǒng)(SoPC),實現(xiàn)高度定制化的嵌入式解決方案。

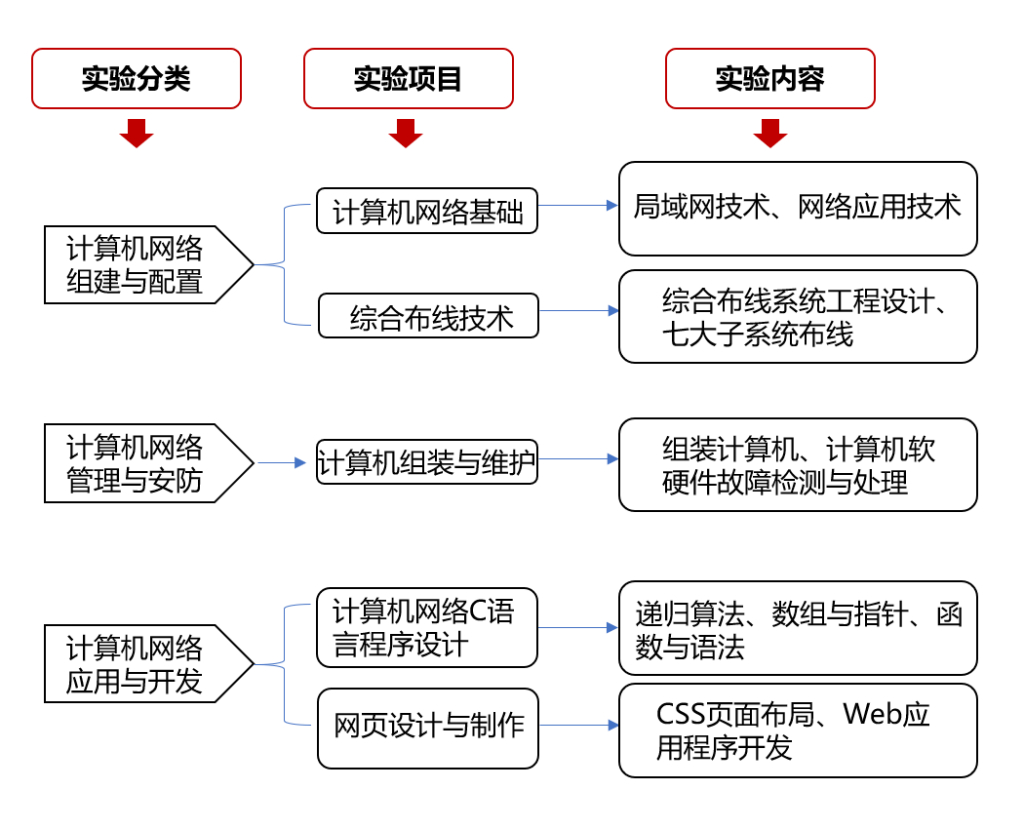

- 教學與科研平臺:為計算機體系結構、數(shù)字邏輯、嵌入式系統(tǒng)等課程提供理想的實踐平臺,讓學生能夠親手設計并驗證CPU、緩存、總線等核心部件,深化對計算機底層工作原理的理解。

###

掌握EDA技術與CPLD/FPGA開發(fā),意味著掌握了將創(chuàng)新算法和系統(tǒng)架構直接轉化為高效硬件實現(xiàn)的能力。這不僅是深入理解計算機系統(tǒng)“從軟到硬”全棧知識的關鍵環(huán)節(jié),更是應對未來智能計算、邊緣計算、定制化芯片等前沿趨勢的核心技能。本教程作為入門指引,期望能激發(fā)學習者的興趣,引導其步入這片充滿挑戰(zhàn)與機遇的技術領域,為未來計算機軟硬件的協(xié)同創(chuàng)新與發(fā)展貢獻力量。

如若轉載,請注明出處:http://www.jinhaohb.cn/product/73.html

更新時間:2026-03-31 21:45:05